Advantest Corporation ha presentato i primi prototipi di una linea di prodotti di nuova generazione dedicati al collaudo e manipolazione automatica di circuiti integrati con strutture 2.5D e 3D basati su tecnologia TSV (Through Silicon Via).

Advantest Corporation ha presentato i primi prototipi di una linea di prodotti di nuova generazione dedicati al collaudo e manipolazione automatica di circuiti integrati con strutture 2.5D e 3D basati su tecnologia TSV (Through Silicon Via).

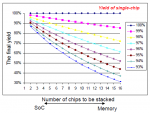

La sovrapposizione di più piastrine di silicio espone al rischio di un eccessivo numero di difetti nel dispositivo completo causato dalla presenza di imperfezioni anche di una sola delle piastrine che compongono la pila di piastrine sovrapposte (stack) tra loro collegate.

Il prototipo della nuova soluzione proposta da Advantest, denominato Dimension, integra un cluster di sistemi di collaudo ad elevato parallelismo con un manipolatore automatizzato capace di trattare singoli die e die 3D Stack.

Il prototipo della cellula di collaudo e manipolazione integrata nella linea di produzione presentato da Anritsu punta a risolvere il problema passando da una metodologia di collaudo mirata a identificare i singoli die funzionanti sul wafer (Known Good Die, o KGD) a una metodologia capace di identificare gli stack completi funzionanti (Known Good Stack, KGS) ridefinendo le aspettative in termini di produttività e di elevatissima resa necessari per produrre economicamente chip con strutture tridimensionali.

Le tecnologie di produzione dei circuiti integrati 2.5D e 3D Stack permettono di ottenere eccellenti miglioramenti in termini di densità, consumo energetico e prestazioni, ma scontrandosi con le difficoltà di manipolazione di die molto fragili, di dover controllare attivante le diverse escursioni di temperatura e di dover gestire in modo integrato la resa del processo (yield) risultante dala sovrapposizione di più chip singoli.

Le soluzioni introdotte con Dimension affrontano tali problemi con la tecnologia SmartDieCarrier (SmtDCTM). Le soluzioni SmtDCTM offrono contemporaneamente funzionalità di pick-and-place per die oltre alla capacità di contatto con passo estremamente ridotto, garantendo allo stesso tempo precisione e manipolazione molto delicata.

Grazie alla gestione in tempo reale della potenza, la funzione Active Thermal Control (ATC) garantisce il rispetto delle condizioni di collaudo come da specifica, con impatto positivo sulla resa di processo.

Le applicazioni della tecnologia 3D TSV offrono potenzalmente prestazioni eccellenti con elevata diminuzione dei consumi ed evidenti vantaggi in termini di riduzione delle dimensioni fisiche.

Ad esempio, l'architettura delle memorie Wide I/O Mobile DRAM definita da JEDEC incrementa di otto volte l’ampiezza di banda e riduce il consumo dell’alimentazione di I/O dal 25 al 50% rispetto alle architetture di DRAM tradizionali.

Tuttavia il mercato odierno richiede contemporaneamente rese di produzione altissime e costi sempre più bassi. La crescita delle DRAM con architettura Wide I/O e di futuri dispositivi eterogenei 3D TSV è subordinata alla possibilità di produrre stack completi funzionanti correttamente (KGS) con eccellente livello qualitativo e resa elevata.

L'architettura proposta da Advantest con Dimension offre una dimostrazione delle soluzioni KGD e KGS necessarie per produrre economicamente i chip per gli smartphone e i tablet di domani, oltre che per router di telecomunicazioni e CPU per supercomputer attualmente in fase di sviluppo.