Il bus PCI Express (PCIe) 6.0 è stato sviluppato per soddisfare le esigenze di trasmissione dati ad alta velocità delle applicazioni emergenti, in particolare i data center che devono supportare la tecnologia 5G.

Il bus PCI Express (PCIe) 6.0 è stato sviluppato per soddisfare le esigenze di trasmissione dati ad alta velocità delle applicazioni emergenti, in particolare i data center che devono supportare la tecnologia 5G.

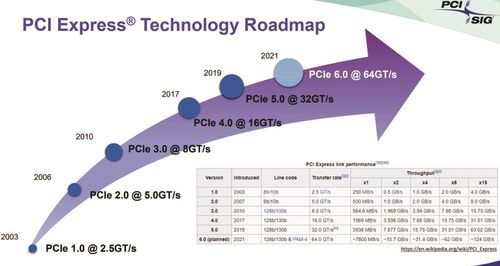

Con il raddoppio della velocità dei dati e il miglioramento di altre specifiche prestazionali (figura 1), lo standard PCIe 6.0 aggiunge ulteriore complessità ai progetti di interconnessione ad alta velocità. Gli sviluppatori che progettano prodotti e sistemi utilizzati in applicazioni ad alta velocità devono verificare le prestazioni delle connessioni utilizzando un approccio che incorpori soluzioni di test in grado di condurre analisi in tempo reale, risparmiando tempo e migliorando la ripetibilità delle prove.

Fig. 1: Evoluzione della velocità di trasmissione dati sul bus PCIe (Per gentile concessione di PCI-SIG)

Fig. 1: Evoluzione della velocità di trasmissione dati sul bus PCIe (Per gentile concessione di PCI-SIG)

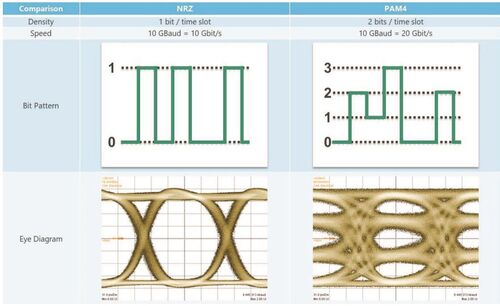

Per soddisfare i requisiti richiesti dai progetti a velocità più elevata, il bus PCIe 6.0 utilizza segnali trasmessi con modulazione PAM4 (Pulse Amplitude Modulation a 4 livelli) a 32 Gbaud.

Le prime cinque generazioni della specifica PCIe hanno utilizzato segnali trasmessi con modulazione NRZ (Non-Return to Zero). La modulazione PAM4 consente di mantenere una lunghezza massima del canale simile a quella definita nelle specifiche PCIe 5.0. Come nel caso di tutte le precedenti generazioni dello standard PCIe, anche la versione PCIe 6.0 è completamente compatibile con le versioni precedenti, quindi anche la modulazione NRZ continuerà ad essere supportata.

I segnali codificati con la modulazione PAM4 raddoppiano la velocità di trasferimento, in quanto nello stesso intervallo di simbolo si trasmettono due bit anziché uno solo.

Se da un lato questo approccio riduce la larghezza di banda per bit, dall'altro degrada la forma d'onda, creando così un occhio molto più piccolo. La Figura 2 mostra la differenza tra i diagrammi ad occhio di due segnali codificati con la modulazione NRZ e PAM 4, nonché la codifica dei bit corrispondente ai diversi stati del segnale.

Fig. 2: Confronto tra codifica dei bit e diagrammi a occhio dei segnali NRZ e PAM4.

Fig. 2: Confronto tra codifica dei bit e diagrammi a occhio dei segnali NRZ e PAM4.

Anche se la frequenza di base è la stessa delle specifica PCIe 5.0 a 32,0 GT/s con codifica NRZ, l’utilizzo della modalità di codifica con modulazione PAM4 nel bus PCIe 6.0 obbliga a utilizzare circuiti e logiche aggiuntive. Ciò è necessario per discriminare i segnali su tre occhi, oltre che per introdurre le modifiche logiche necessarie a gestire la modalità Flow Control Unit (FLIT).

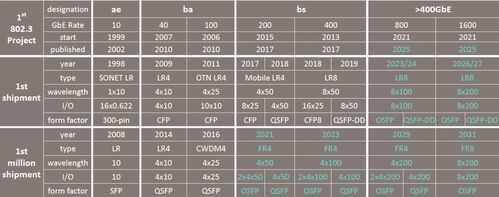

Un'altra tecnologia che sta influenzando i progetti delle connessioni ad alta velocità e che gli sviluppatori devono prendere in considerazione è Ethernet. Nei progetti attuali si utilizzano connessioni 400 GbE, mentre i prodotti e i sistemi di prossima generazione in fase di sviluppo utilizzeranno connessioni 800 GbE o addirittura 1,6 TbE.

La Figura 3 mostra le tappe fondamentali di sviluppo dello standard Ethernet, che ha continuato a soddisfare le crescenti esigenze di trasferimento dei dati ad alta velocità.

Fig. 3: L'evoluzione dello standard Ethernet (Immagine per gentile concessione del gruppo di studio 802.3 Beyond 400 G)

Fig. 3: L'evoluzione dello standard Ethernet (Immagine per gentile concessione del gruppo di studio 802.3 Beyond 400 G)

L'integrazione delle connessioni 400 GbE / 800 GbE nei progetti emergenti ad alta velocità aggiunge ulteriore sfide da affrontare nelle attività di verifica delle prestazioni. Ad esempio, quando si effettuano misure su connessioni 400 GbE / 800 GbE, il rapporto segnale/rumore (SNR) è più critico rispetto alle tecnologie precedenti.

La segnalazione PAM4 allevia la perdita dovuta al canale, perché lavora a metà frequenza con due bit trasportati per ciascuno slot temporale. Un effetto collaterale, tuttavia, è la riduzione di 10 dB dell'SNR.

I tre occhi associati ai segnali PCIe 6.0 si trovano nello stesso slot temporale corrispondente a un periodo di simbolo. Il risultato è che l'altezza e la larghezza dell'occhio sono ridotte. Per questo motivo, il tasso di errore di bit (BER) risulta considerevolmente superiore utilizzando la modulazione PAM4.

Nello standard PCIe 6.0, il tasso di errore BER (Bit Error Rate) è una combinazione del tasso di errore del primo bit FBER (First Bit Error Rate), della correlazione degli errori in una corsia e della correlazione degli errori tra le corsie.

Il tasso di errore FBER è la probabilità che si verifichi un primo bit errato (di un’eventuale sequenza) sul ricevitore. L’organizzazione PSI-SIG ha condotto studi approfonditi prima di stabilire che la probabilità in PCIe 6.0 valga 1,0E(-6).

Lo standard PCIe 6.0 prevede di utilizzare uno specifico approccio per mantenere la bassa latenza necessaria per le applicazioni ad alta velocità. Integra un FBER più basso con una tecnica di correzione degli errori FEC (Forward Error Correction) a bassa latenza per effettuare una prima correzione degli errori.

Il FEC è una tecnica di codifica avanzata che trasmette anche i dati supplementari necessari per correggere gli errori attraverso il collegamento PAM4 ed è fondamentale per garantire la qualità della trasmissione. È anche un elemento essenziale per i test, a causa del degrado del rapporto segnale/rumore SNR causato dall’utilizzo della modulazione PAM4.

Una volta eseguita la correzione degli errori mediante FEC, un robusto controllo di ridondanza ciclica (CRC) rileva gli errori rimasti. Il risultato è un meccanismo di ritrasmissione a livello di collegamento che garantisce il rispetto dei requisiti di bassa latenza, elevata larghezza di banda e alta affidabilità.

PCI-SIG ha stabilito un requisito per la correzione FEC a bassa latenza di <2 ns per PCIe 6.0, che deve far parte della latenza complessiva del segnale specificata, pari a <10 ns. La correzione FEC si basa su un numero fisso di simboli. Per questo motivo, è semplice passare all’utilizzo della modalità di trasferimento FLIT (FLow controller unIT), anch’essa basata su blocchi di dimensioni fisse.

Un approccio consigliato per valutare efficacemente le prestazioni è quello di stabilire una soglia di errore dei simboli tramite FEC. In questo modo, i tecnici hanno un controllo più ampio sulle condizioni di errore che influenzano i pattern durante l'acquisizione, ignorando gli eventi insignificanti che vengono normalmente corretti nello strato FEC.

Per impostare una soglia, un tester BERT (Bit Error Rate Tester) genera un segnale PAM4 che viene inviato all'ingresso del ricevitore del dispositivo in prova (DUT). Il DUT determina lo stato logico del segnale di ingresso e lo invia all'uscita del suo trasmettitore, dove verrà inoltrato al BERT per l'analisi degli errori.

Il rilevatore di errori del BERT determina se la decisione presa dal ricevitore del DUT è corretta. Per ottenere risultati rilevanti, i profili di jitter e rumore del BERT devono essere conformi agli standard. Per misurare in modo affidabile l'errore dei simboli tramite FEC, il BERT utilizzato per effettuare le misure deve avere un rilevatore di errori PAM4 da 116 Gbit/s ad alta sensibilità.

Quando si esegue il test, è importante notare che un singolo errore casuale non è significativo come un errore che si verifica in sequenza in un burst. Un'altra considerazione è che alcuni burst di errori non possono essere corretti a livello FEC oltre un certo limite.

La post-elaborazione deve essere eseguita oltre tale limite, per aiutare a determinare il motivo per cui il DUT potrebbe leggere male un simbolo in ingresso. Con questo approccio, gli sviluppatori possono valutare un dispositivo utilizzando sequenze di segnali pseudocasuali (PRBS) standard e basando la cattura degli errori su eventi che potrebbero essere problematici in un ambiente che usa il FEC.

Se i dati in ingresso vengono catturati quando il numero di errori nei simboli corretti dal FEC supera la soglia impostata, è necessario effettuare una misura della cattura dei simboli per determinare quale flusso di dati causa gli errori non correggibili. Un burst di errori non correggibile è definito come una sequenza di errori di simbolo FEC Reed-Solomon (RS) che totalizza più di 16 errori per parola di codice.

Fig. 4: Una soluzione di test con capacità di acquisizione dei simboli FEC in tempo reale offre molteplici vantaggi nella verifica dei progetti ad alta velocità.Una soluzione di test con un BERT (figura 4) capace di acquisire i simboli FEC in tempo reale offre una maggiore ripetibilità e sicurezza nelle misure.

Fig. 4: Una soluzione di test con capacità di acquisizione dei simboli FEC in tempo reale offre molteplici vantaggi nella verifica dei progetti ad alta velocità.Una soluzione di test con un BERT (figura 4) capace di acquisire i simboli FEC in tempo reale offre una maggiore ripetibilità e sicurezza nelle misure.

Gli sviluppatori possono monitorare le variazioni degli errori di bit e degli errori di simbolo corretti tramite FEC con le deviazioni dell'ampiezza di ingresso e le condizioni di jitter nel momento in cui si verificano, per una migliore valutazione delle condizioni in cui il numero di errori di simbolo supera la capacità di correzione degli errori della codifica FEC.

I dati di ingresso vengono acquisiti quando il numero di errori di simbolo corretti dal FEC supera la soglia impostata, fino a 128 eventi di burst error. Di conseguenza, le cause degli errori non correggibili possono essere analizzate in modo più efficiente a partire dai dati acquisiti.

L'integrazione della tecnologia PAM4 in PCIe 6.0 ha permesso alle interconnessioni di nuova generazione di soddisfare i requisiti delle applicazioni ad alta velocità emergenti.

Una soluzione di test completa che includa funzionalità di analisi in tempo reale dei dati con codifica del FEC aiuta gli sviluppatori a verificare i progetti e ad avere maggiore fiducia nelle prestazioni dei loro prodotti.

*Hiroshi Goto ricopre la posizione di Product Manager e Business Development Manager per le soluzione ottiche e ad alta velocità di Anritsu